2026年3月开班计划:

FPGA逻辑开发班、FPGA测试定向班

开班时间:3月30日(预科)

开班地点:成都基地(成都ai创新中心)

冬令营开班计划:

开班时间:7月6日(暂定)

开班地点:成都基地(成都ai创新中心)

集成电路行业岗位细分与 FPGA 工程师定位 从应用前景视角解读 Gartner 2026 十大关键技术趋势

集成电路行业岗位细分与 FPGA 工程师定位 从应用前景视角解读 Gartner 2026 十大关键技术趋势

Gartner 每年发布的《十大关键战略技术趋势》报告,为全球企业技术变革与业务转型提供核心指引。2026 年版报告将关键技术趋势划分为 Architect(架构者)、Synthesist(整合者)、Vanguard(守卫者)三大类别,围绕 AI 平台与基础设施、AI 应用与编排、安全与信任治理三条主线展开。

在集成电路产业高速发展的当下,明确行业岗位细分及核心岗位价值,对把握技术趋势、培养适配人才至关重要。FPGA(现场可编程门阵列)作为具备高度可定制性、并行处理能力强、低延迟响应等核心优势的集成电路,其灵活适配特性与 2026 年多数关键技术趋势的需求高度契合,而 FPGA 工程师也成为连接技术趋势与产业落地的关键人才。本文将先梳理集成电路行业岗位细分,明确 FPGA 工程师在芯片应用领域的核心位置,再深度解读十大技术趋势下 FPGA 的应用价值落地路径。

一、集成电路行业岗位细分全景

集成电路产业是典型的技术密集型行业,产业链涵盖芯片设计、芯片制造、芯片封装测试、芯片应用四大核心环节,各环节岗位分工明确、协同联动,共同构成产业发展的人才支撑体系。

(一)芯片设计环节:产业创新的源头核心

该环节聚焦芯片功能定义与架构实现,是决定芯片性能与差异化的关键,细分岗位包括:

前端设计类:系统架构师、算法工程师、逻辑设计工程师(Verilog/VHDL 开发)、仿真验证工程师,负责芯片功能建模、代码编写与逻辑正确性验证;

后端设计类:布局布线工程师、时序分析工程师、物理验证工程师,负责将前端逻辑转化为可制造的物理版图,保障芯片时序性能与生产可行性;

配套支撑类:EDA 工具工程师、IP 核设计工程师,为芯片设计提供工具链支持与模块化 IP 解决方案。

(二)芯片制造环节:技术落地的核心载体

该环节依托晶圆厂完成芯片物理制造,岗位围绕 “工艺实现” 与 “良率提升” 展开,包括:

工艺研发类:光刻工艺工程师、蚀刻工艺工程师、掺杂工艺工程师,负责半导体制造工艺的研发与优化;

生产管控类:晶圆制造工程师、良率提升工程师(Yield Engineer)、设备维护工程师,保障晶圆生产线稳定运行,提升芯片生产良率。

(三)芯片封装测试环节:芯片可靠性的最后防线

该环节连接芯片制造与终端应用,核心目标是确保芯片性能稳定、符合应用需求,细分岗位有:

封装设计类:封装工程师、基板设计工程师,根据应用场景选择封装方案(如 BGA、QFP、SiP),优化芯片散热与信号完整性;

测试验证类:芯片测试工程师、ATE 测试开发工程师,负责设计测试方案,通过自动化测试设备验证芯片功能、性能与可靠性。

(四)芯片应用环节:技术价值的最终实现

该环节是集成电路产业与下游行业的桥梁,核心任务是将芯片技术转化为满足行业需求的解决方案,细分岗位包括:

嵌入式开发类:嵌入式软件工程师、驱动开发工程师,负责芯片驱动程序编写与嵌入式系统搭建;

硬件集成类:硬件电路设计工程师、系统集成工程师,负责基于芯片的硬件电路设计与整机系统集成;

行业方案类:FPGA 工程师、AI 加速方案工程师、工业控制方案工程师,针对特定场景提供芯片应用的定制化解决方案。

二、FPGA 工程师在芯片应用领域的核心位置

在集成电路行业岗位体系中,FPGA 工程师属于芯片应用环节的核心技术岗位,同时兼具 “芯片应用执行者” 与 “芯片设计支撑者” 的双重属性,是连接芯片技术与行业场景的关键枢纽。

(一)核心定位:芯片应用场景的定制化解决方案专家

FPGA 的可编程特性使其无需流片即可实现硬件功能重构,这一优势让 FPGA 工程师能够快速响应下游行业的定制化需求。不同于通用芯片应用工程师,FPGA 工程师需要兼具硬件逻辑设计能力与软件系统开发能力:既懂 Verilog/VHDL 硬件描述语言,能完成 FPGA 内部逻辑电路设计;又掌握 C/C++ 等编程语言,能实现软硬件协同开发。

在产业链中,FPGA 工程师直接对接工业自动化、通信、人工智能、汽车电子等下游行业客户,将 FPGA 芯片的技术优势转化为具体的行业应用方案,例如工业质检中的机器视觉加速方案、5G 基站中的信号处理方案、自动驾驶中的实时数据处理方案等,是 FPGA 技术落地的核心执行者。

(二)延伸定位:芯片设计环节的重要支撑力量

除了芯片应用,FPGA 工程师还在芯片设计环节扮演关键角色。在 ASIC、SoC、Chiplet 等定制芯片流片前,FPGA 是唯一可承载高频系统级验证的硬件平台。FPGA 工程师通过搭建 FPGA 验证平台,对前端设计的芯片逻辑进行全功能验证,及时发现设计缺陷,大幅降低芯片流片风险与成本。这一工作模式使得 FPGA 工程师成为芯片设计环节的重要支撑,衔接前端设计与后端制造,提升芯片研发效率。

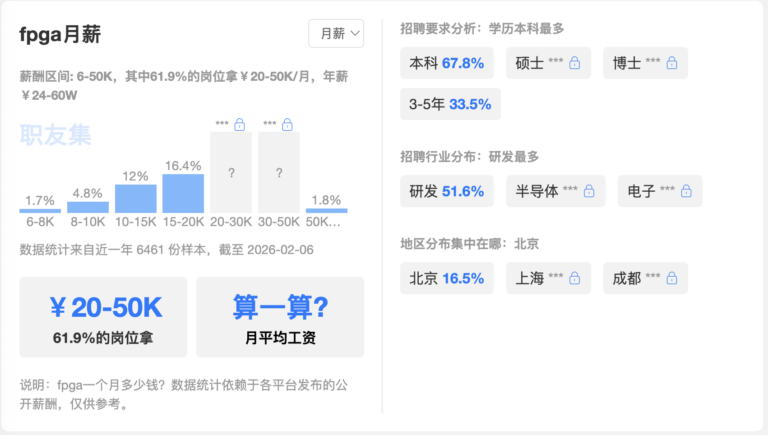

(三)岗位价值:技术趋势驱动下的需求增长核心

随着 AI、工业互联网、边缘计算等技术的发展,下游行业对低延迟、高并行、可定制的硬件解决方案需求激增,FPGA 工程师的岗位价值愈发凸显。尤其是在 Gartner 2026 十大技术趋势的推动下,FPGA 的应用场景持续拓展,对 FPGA 工程师的能力要求也从传统的逻辑设计,向AI 加速、安全防护、云边端协同等新兴领域延伸,岗位需求呈现爆发式增长态势。

三、Architect(架构者)类趋势:FPGA 筑牢技术架构底座,工程师成架构优化核心人才

Architect 类趋势聚焦技术架构的重构与升级,核心包括 AI 原生开发平台、AI 超级计算、分布式云原生三大方向,旨在通过底层架构优化支撑上层智能应用的规模化落地。FPGA 凭借可编程硬件特性,成为这类趋势中不可或缺的核心支撑器件,而 FPGA 工程师则是架构优化与落地的核心人才。

1. AI 原生开发平台:FPGA 开发流程的智能化革新,催生智能开发工程师岗位

Gartner 将 AI 原生开发平台列为 2026 年首要架构类趋势,其核心是通过大模型赋能开发全流程,实现工程效率的指数级提升。这一趋势为 FPGA 开发带来革命性机遇,也对 FPGA 工程师的能力提出新要求。

技术价值落地:一方面,FPGA/EDA 工具链将被全面纳入 AI 原生开发体系,工程师只需描述功能需求,AI 即可自动化完成工程脚本生成、约束模板配置、IP 核选型、接口文档撰写等重复性工作,同时实现代码的自动测试与优化,大幅缩短 FPGA 开发周期;另一方面,FPGA 将成为 AI 原生开发的核心验证载体,随着芯片设计迭代频率提升,FPGA 作为唯一可承载高频系统级验证的硬件,将成为 ASIC、SoC、Chiplet 等芯片流片前的关键验证平台,AI 原生开发平台的普及将进一步放大这一需求。

岗位能力需求:FPGA 工程师需要掌握 AI 原生开发工具链的使用方法,具备将 AI 生成的代码转化为可落地的 FPGA 逻辑设计能力,同时熟悉芯片验证流程,能够搭建高效的 FPGA 验证平台,这一趋势将催生 “FPGA 智能开发工程师” 这一新兴岗位。

2. AI 超级计算:FPGA 破解算力与效率瓶颈,加速工程师成稀缺人才

2026 年全球 AI 算力需求将实现规模倍增,权威数据显示,当年全球智能算力规模将达到 2022 年的 8-10 倍,其中推理算力占比首次超过训练算力,达到 66%。AI 超级计算对算力密度、延迟控制、能耗效率提出严苛要求,FPGA 在此场景中展现独特价值,FPGA 加速工程师成为稀缺人才。

技术价值落地:其一,作为数据预处理核心,FPGA 可部署于网络接口与 GPU/CPU 之间,在数据进入核心计算单元前完成解包、清洗、格式转换等内联处理,减少 GPU 无效算力消耗,提升整体集群效率;其二,在 AI 数据中心网络构建中,FPGA 可实现 RoCE/IB 协议卸载、流量整形、虚拟化隔离等功能,是打造高性能智能网卡(Smart NIC)的核心组件,有效解决 AI 集群的带宽瓶颈与延迟问题;其三,针对边缘端 AI 推理场景,FPGA 的低功耗、高并行特性使其成为边缘智能节点的理想选择,适配工业质检、自动驾驶等实时性要求极高的推理任务。

岗位能力需求:FPGA 工程师需要精通 AI 推理加速算法的硬件实现,熟悉智能网卡、边缘计算节点的架构设计,具备 FPGA 与 GPU/CPU 协同优化的能力,这类 “FPGA AI 加速工程师” 将成为 AI 超级计算领域的核心人才。

3. 分布式云原生:FPGA 赋能云边端协同架构,系统集成工程师需求激增

分布式云原生架构强调云、边、端算力的协同调度,以适配不同场景的计算需求。FPGA 的可编程特性使其能够灵活适配云边端不同的硬件环境与任务需求,推动 FPGA 系统集成工程师需求激增。

技术价值落地:在云端,FPGA 可通过虚拟化技术实现多租户资源隔离,为不同用户提供定制化的硬件加速服务;在边缘端,FPGA 凭借小尺寸、低功耗优势,可集成于工业网关、边缘服务器中,承担实时数据处理、协议转换、本地推理等任务;在端侧,FPGA 可嵌入智能终端设备,实现轻量化 AI 功能的快速部署,形成 “云侧训练 – 边侧推理 – 端侧执行” 的全链路协同支撑。

岗位能力需求:FPGA 工程师需要具备云边端协同架构的设计能力,熟悉 FPGA 虚拟化技术与边缘计算节点的集成方案,能够根据不同场景需求定制 FPGA 应用解决方案,这类 “FPGA 系统集成工程师” 将成为分布式云原生架构落地的关键力量。

四、Synthesist(整合者)类趋势:FPGA 驱动跨场景智能融合,跨界工程师成核心纽带

Synthesist 类趋势聚焦技术的跨领域整合与价值释放,核心包括特定领域语言模型(DSLM)、物理 AI、多智能体系统(MAS)三大方向,旨在打破技术壁垒,实现智能能力与物理世界、业务场景的深度融合。FPGA 的 “感控一体” 与灵活适配特性,成为这类趋势落地的关键支撑,兼具硬件与行业知识的跨界 FPGA 工程师成为核心纽带。

1. 特定领域语言模型(DSLM):FPGA 开发的 “智能编译器” 革新,提升工程师设计效率

DSLM 是基于行业专属数据集训练的垂直领域 AI 模型,相比通用大模型具备更高的准确性与合规性。在 FPGA 开发领域,DSLM 将带来颠覆性变革,大幅提升 FPGA 工程师的设计效率。

技术价值落地:一方面,面向 RTL/Verilog/VHDL 等硬件描述语言的 DSLM 将成为新一代 “智能编译器”,能够自动生成可综合代码、修复逻辑错误、派生测试用例,并基于设计意图给出面积、时延、功耗优化建议,大幅降低 FPGA 开发门槛;另一方面,围绕 FPGA/EDA 构建专用 RAG(检索增强生成)语料体系,整合海量工程文档、历史项目代码、错误案例等资源,将使 DSLM 具备 “高级工程师级” 的设计经验,进一步提升开发效率与设计质量。对于国产 FPGA 与 EDA 生态而言,自主可控的硬件 DSLM 将成为构建差异化竞争优势的重要抓手。

岗位能力需求:FPGA 工程师需要具备将 DSLM 生成的代码进行优化与验证的能力,熟悉 FPGA 设计的性能优化方法,能够结合行业需求调整模型生成的设计方案,提升 FPGA 设计的可靠性与实用性。

2. 物理 AI:FPGA 构建 “感知 – 决策 – 行动” 闭环核心,工业 FPGA 工程师需求旺盛

物理 AI 通过整合传感器、执行器与 AI 模型,将智能能力延伸至物理世界,广泛应用于机器人、无人机、智能装备等领域。Gartner 预测,到 2028 年全球前十名 AI 供应商中将有一半推出物理 AI 产品。FPGA 在物理 AI 系统中承担 “感控一体” 核心角色,推动工业 FPGA 工程师需求旺盛。

技术价值落地:其一,可在单芯片内整合 MIPI、LVDS、以太网等多种高速接口,实现多传感器数据的实时融合与预处理;其二,支持轻量神经网络推理与运动控制逻辑并行运行,满足物理 AI 系统 “感知 – 决策 – 行动” 的低延迟闭环需求;其三,在车载、工业安全等对功能安全有严格要求的场景中,FPGA 可实现冗余通道、投票逻辑等安全机制,轻松适配 SIL/ASIL 等安全标准,将智能控制与安全监控集成于同一硬件架构。

岗位能力需求:FPGA 工程师需要熟悉工业传感器接口协议与运动控制算法,具备 FPGA 与物理 AI 系统的集成能力,能够设计符合功能安全标准的 FPGA 逻辑,这类 “工业 FPGA 工程师” 将成为智能制造领域的核心人才。

3. 多智能体系统(MAS):FPGA 保障实时协同与可靠控制,协同控制工程师成关键

MAS 由多个具备自主决策能力的智能体组成,通过协同交互完成复杂任务,在工业自动化、智能交通等领域应用前景广阔。Gartner 数据显示,2024 年一季度至 2025 年二季度,关于 MAS 的企业咨询量增长 1445%,反映出市场需求的快速攀升。FPGA 在 MAS 中具备不可替代的优势,FPGA 协同控制工程师成为系统稳定运行的关键。

技术价值落地:其高并行处理能力可支持多智能体间的实时数据交互与协同决策;确定性时延与低抖动特性能够保证控制指令的精准执行,避免多智能体协同中的时序混乱;同时,FPGA 可集成安全加密模块,保障智能体间数据传输的机密性与完整性,为 MAS 的规模化部署提供安全可靠的硬件支撑。

岗位能力需求:FPGA 工程师需要具备多智能体协同控制算法的硬件实现能力,熟悉实时通信协议与安全加密技术,能够设计低延迟、高可靠的 FPGA 协同控制逻辑,满足 MAS 系统的严苛要求。

五、Vanguard(守卫者)类趋势:FPGA 构建硬件级安全屏障,安全 FPGA 工程师成新热点

Vanguard 类趋势聚焦安全与信任体系的构建,核心包括前置式主动网络安全、隐私增强计算、可信 AI 三大方向,旨在应对 AI 驱动的新型安全威胁。FPGA 凭借可编程硬件特性,能够构建灵活、高效的硬件级安全防护体系,安全 FPGA 工程师成为新的岗位热点。

1. 前置式主动网络安全:FPGA 实现实时威胁阻断,网络安全 FPGA 工程师需求增长

前置式主动网络安全突破传统 “检测 – 响应” 的被动防御模式,通过 AI 技术在攻击发生前实现预测、干扰与化解。Gartner 预测,到 2029 年缺乏主动式安全能力的技术产品将失去市场竞争力。FPGA 在此场景中表现出显著优势,推动网络安全 FPGA 工程师需求增长。

技术价值落地:基于 FPGA 的智能网卡(Smart NIC)可对海量网络流量进行线速分析,实时识别异常行为与攻击特征,在攻击流量到达核心服务器前完成阻断,避免传统 CPU-based 安全设备的性能瓶颈;同时,FPGA 的可编程特性支持安全算法的灵活更新,能够快速适配新型网络威胁,为网络安全提供持续迭代的硬件级防护能力。

岗位能力需求:FPGA 工程师需要熟悉网络安全协议与攻击检测算法,具备 FPGA 智能网卡的设计与优化能力,能够实现线速流量分析与实时威胁阻断逻辑,这类 “网络安全 FPGA 工程师” 将成为网络安全领域的新兴人才。

2. 隐私增强计算:FPGA 打造定制化可信执行环境,安全加密 FPGA 工程师成稀缺

隐私增强计算旨在在保障数据安全与隐私的前提下实现数据价值挖掘,是数字经济发展的关键支撑。FPGA 可通过可编程逻辑与片上存储资源,构建定制化的硬件级可信执行环境(TEE),安全加密 FPGA 工程师成为稀缺人才。

技术价值落地:在 FPGA 芯片内划分隔离的逻辑分区,将敏感数据与 AI 模型的运行封装其中,形成比通用 CPU/GPU 更细粒度的安全边界;同时,可集成国密算法(SM2/SM3/SM4)、后量子密码(PQC)等加密模块,实现数据采集、处理、传输全链路的加密保护。这一特性使其在金融、政务、军工等对数据安全与国产可控有强需求的领域具备独特优势。

岗位能力需求:FPGA 工程师需要精通国密算法与后量子密码的硬件实现,熟悉可信执行环境的架构设计,能够构建高安全等级的 FPGA 加密逻辑,满足隐私增强计算的严苛要求。

3. 可信 AI:FPGA 保障模型安全与可追溯,可信 AI FPGA 工程师潜力凸显

可信 AI 要求 AI 模型的训练、推理过程具备可解释性、可追溯性与安全性,避免模型被篡改或产生偏见。FPGA 可从硬件层面为可信 AI 提供保障,可信 AI FPGA 工程师的岗位潜力凸显。

技术价值落地:在模型推理阶段,FPGA 可对输入数据与模型参数进行硬件级校验,防止数据污染与模型篡改;通过记录推理过程中的硬件运行日志,实现推理结果的全链路追溯;同时,FPGA 的并行计算能力可支持 AI 模型的可解释性分析,提升模型决策的可信度。

岗位能力需求:FPGA 工程师需要具备 AI 模型推理的硬件实现能力,熟悉模型校验与日志记录的逻辑设计,能够构建可追溯、高可信的 FPGA 推理平台,满足可信 AI 的应用需求。

六、FPGA 工程师岗位前景总结与展望

从集成电路行业岗位细分来看,FPGA 工程师处于芯片应用领域的核心位置,同时兼具芯片设计支撑的延伸价值,是连接芯片技术与下游行业的关键人才。而从 Gartner 2026 十大关键技术趋势的解读可以看出,FPGA 的核心优势与架构重构、智能融合、安全防护三大主线高度契合,在 AI 原生开发、超级计算、物理 AI、主动安全等关键场景中具备不可替代的应用价值。

技术趋势的推进正推动 FPGA 工程师岗位向专业化、跨界化、高端化方向发展:

专业化方面,AI 加速、网络安全、可信 AI 等细分领域催生了一批专精于特定技术的 FPGA 工程师岗位;

跨界化方面,FPGA 工程师需要兼具硬件设计、软件开发与行业知识,成为跨领域的复合型人才;

高端化方面,随着国产 FPGA 与 EDA 生态的完善,具备自主创新能力的 FPGA 工程师将成为产业发展的核心力量。

值得注意的是,2026 年商业航天领域的太空数据中心计划(如中国星网 “太空机房”)将陆续落地,抗辐照 FPGA 作为保障轨上 AI 服务器稳定运行的核心器件,将迎来爆发式增长机遇,对应的 “抗辐照 FPGA 工程师” 将成为新的岗位增长点;同时,边缘 AI 市场的快速扩张也将推动 FPGA 与 NPU、GPU 的架构卡位竞争,其可编程优势在小批量、定制化场景中将持续凸显。

未来,随着技术趋势与产业需求的深度融合,FPGA 工程师的岗位价值将进一步提升,成为推动集成电路产业升级与数字经济发展的关键人才支撑。