往期学员作品

沉浸式做项目

在当前高校保研竞争中,学科竞赛经历已成为提升综合竞争力的关键因素,尤其在电子信息、自动化等工科领域,全国大学生电子设计竞赛(含FPGA专项赛事)凭借其高含金量,被多所高校纳入保研评审的重要参考体系。本文结合部分高校保研政策中对电赛的具体要求,解析竞赛经历在保研中的核心价值,并介绍成电国芯FPGA赛事课程如何通过系统化训练,帮助学生从大一开始积累竞赛优势,为保研奠定坚实基础。

尽管多数高校未在保研政策中明确标注“FPGA赛事加分细则”,但通过梳理燕山大学、电子科技大学、成都信息工程大学、武汉大学等高校的官方通知及保研评审规则,可发现电赛经历主要通过以下维度影响保研结果:

多数高校的保研评审包含“学业成绩+综合素质”两部分,其中“综合素质”模块中,电赛经历常与学术论文、专利等并列,成为“创新实践”维度的核心内容。例如,某985高校明确“国家级学科竞赛一等奖可等同1篇核心期刊论文成果”,直接提升综合排名竞争力。

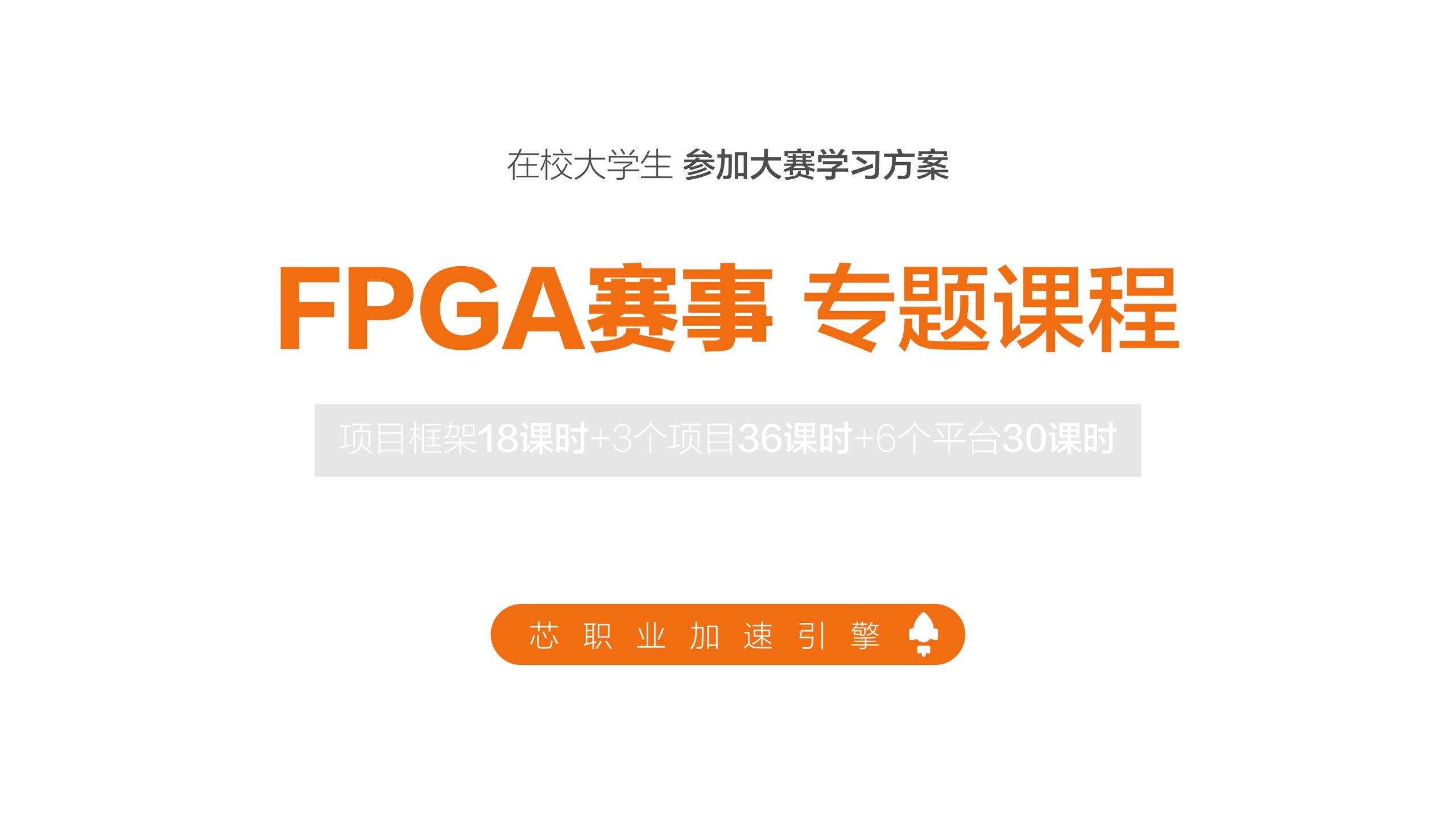

针对电子信息专业学生早期规划竞赛、积累项目经验的需求,成电国芯FPGA赛事课程通过“O2O教学模式+系统化内容设计”,帮助学生从大一开始夯实基础,提前锁定竞赛优势,为保研积累核心素材。其课程优势主要体现在以下三方面:

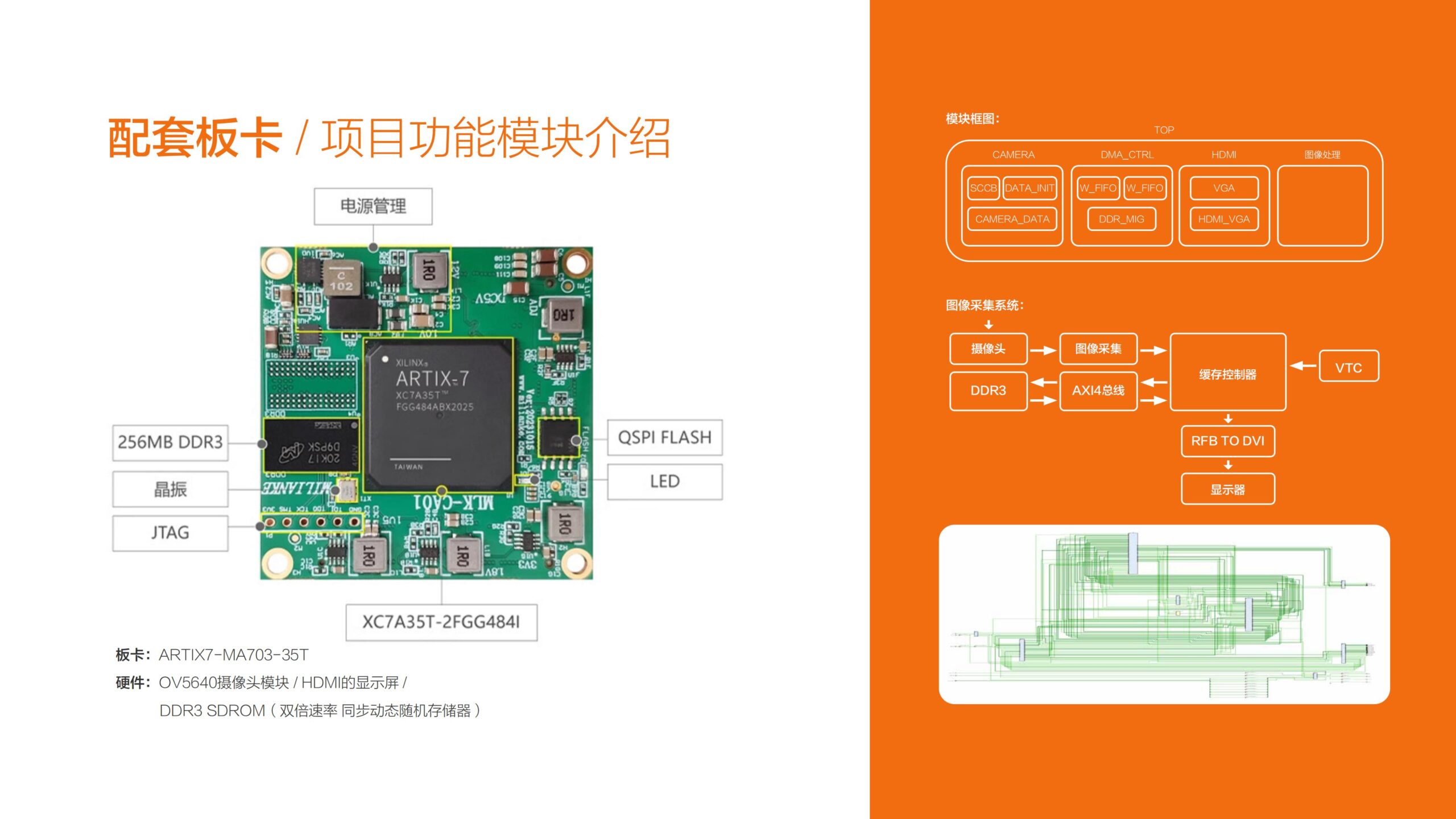

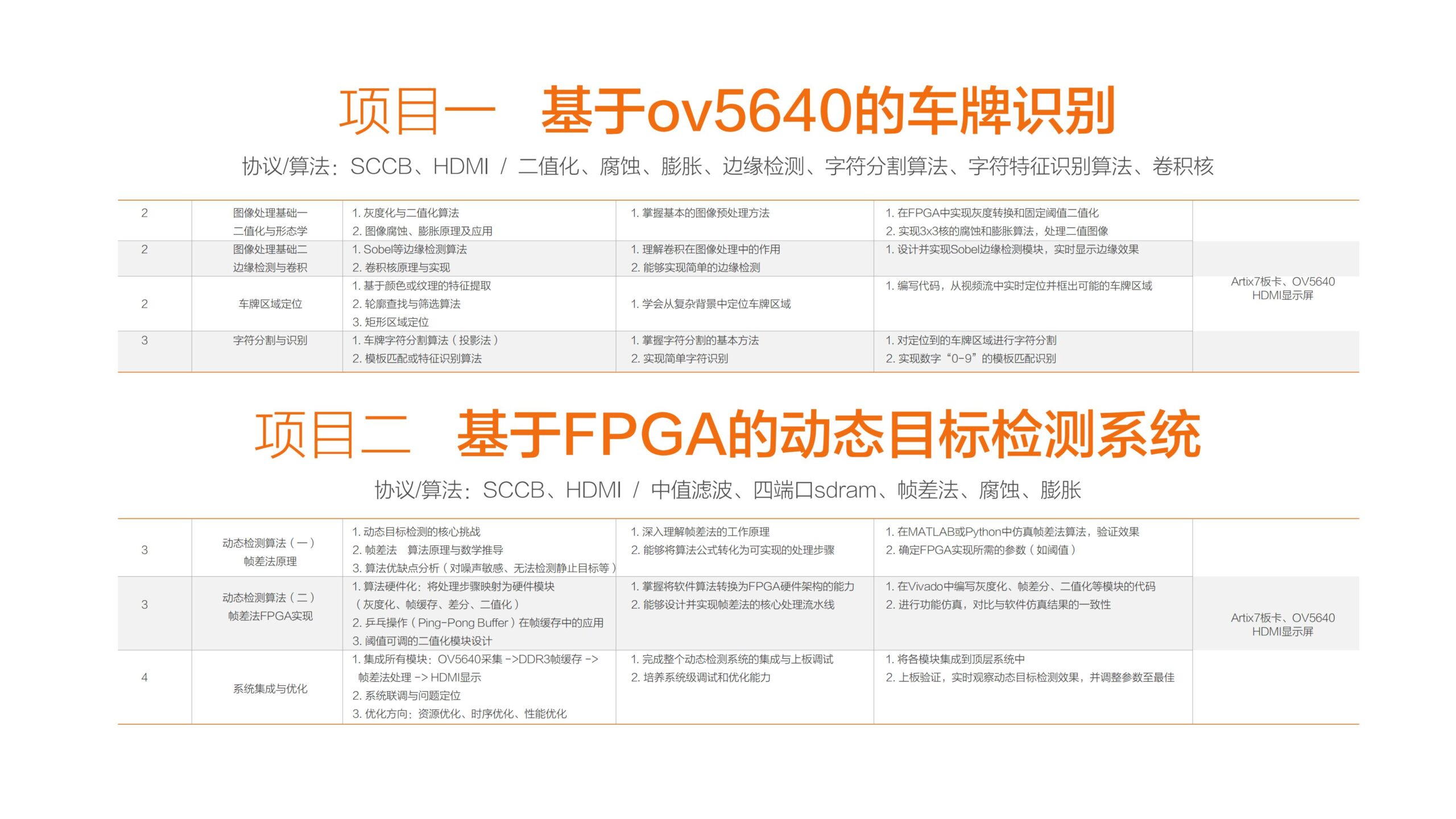

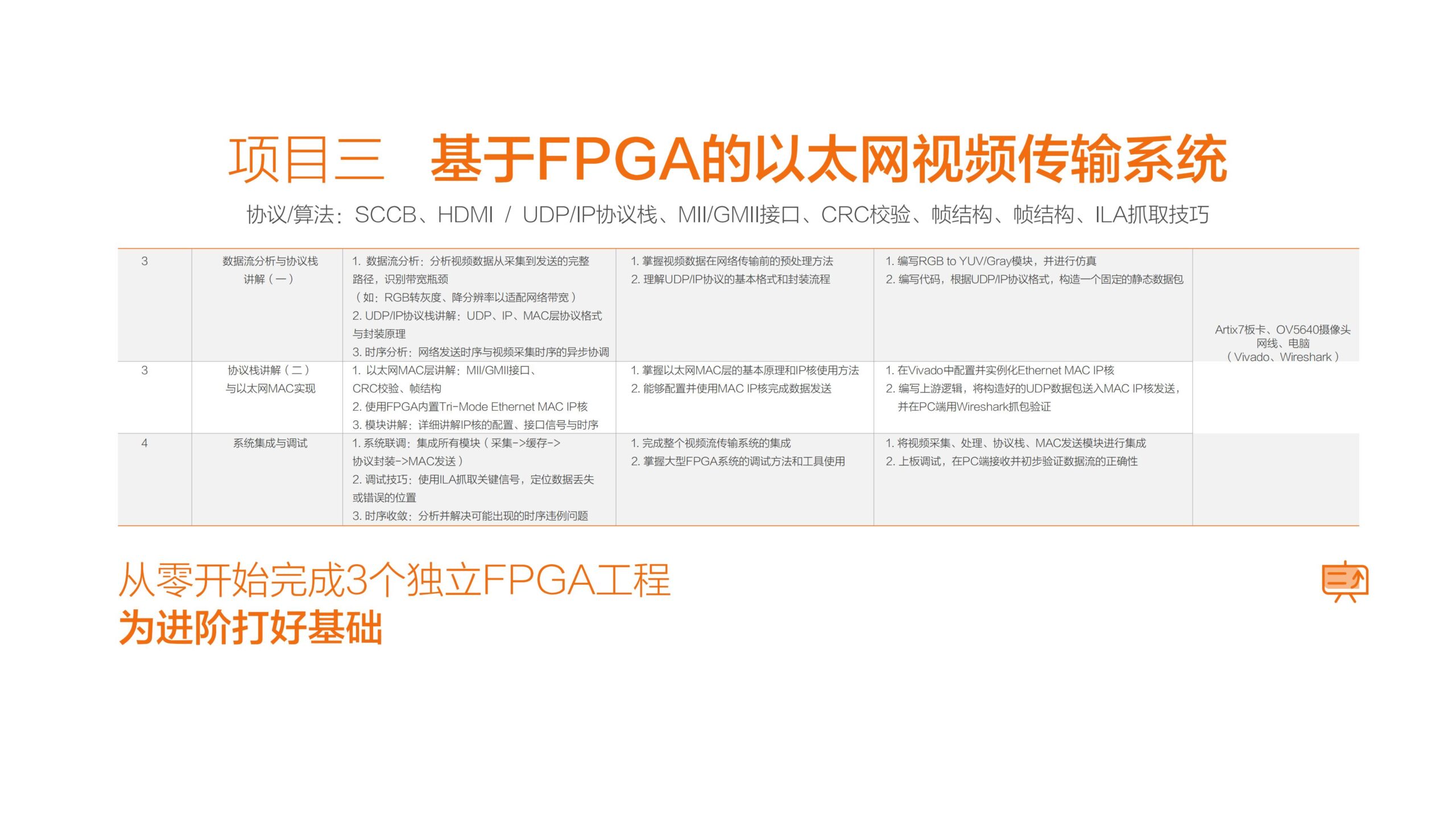

课程总时长84课时,采用“项目框架+实战项目+平台应用”三段式结构:

课程面向大一年级开放,通过“早起步、长周期”培养,帮助学生:

结合高校政策与课程优势,建议学生从以下维度规划竞赛与保研路径:

结语:在保研竞争日趋激烈的背景下,电子设计竞赛已从“加分项”升级为“必备项”。通过系统化课程提前规划、积累高质量项目经验,不仅能在竞赛中脱颖而出,更能为保研评审注入“硬实力”背书。成电国芯FPGA赛事课程以其“早起步、强实战、全流程”的培养模式,为学生搭建了从基础学习到竞赛获奖、再到保研成功的完整路径,助力实现升学目标。

(注:文中高校政策基于公开竞赛通知及保研评审规则整理,具体加分细则请以学校当年官方文件为准。)